| Content | |

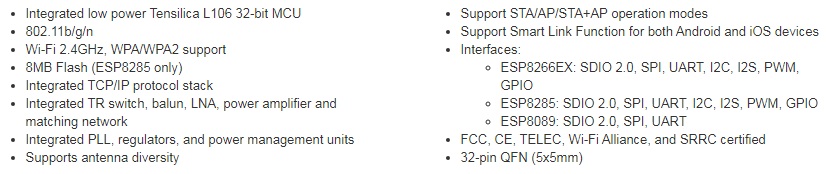

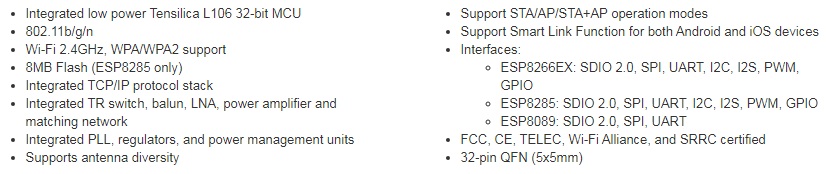

ESP8285 delivers highly integrated Wi-Fi SoC solutions to meet users’ continuous demands for efficient power usage, compact design and reliable performance in the Internet-of-Things industry. With the complete and self-contained Wi-Fi networking capabilities, ESP8285 can perform either as a standalone application or as the slave to a host MCU. When ESP8285 hosts the application, it promptly boots up from the flash. The integrated high-speed cache helps to increase system performance and optimize system memory. Also, ESP8285 can be applied to any microcontroller design as a Wi-Fi adaptor through SPI/SDIO or UART interfaces.

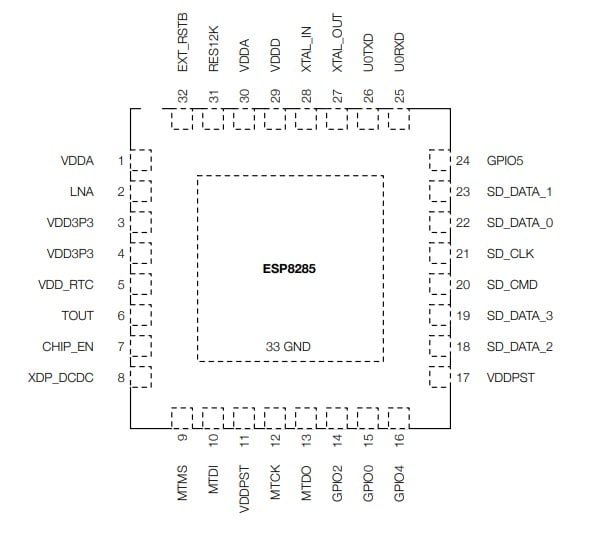

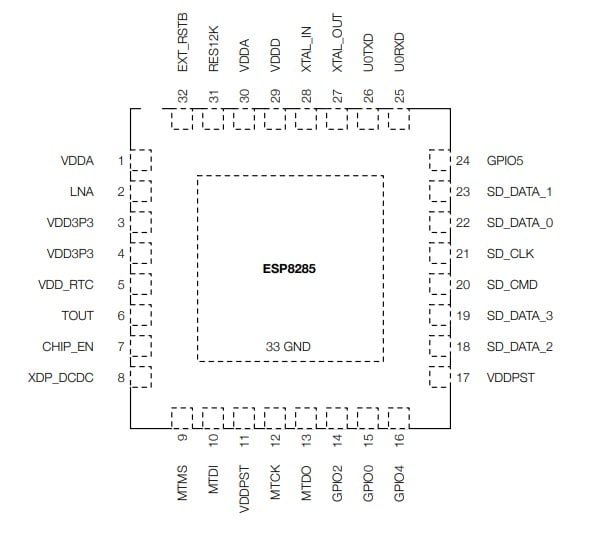

Pin Diagram

Features:

Package Includes:

1 x ESP8285 QFN32 IC Chip

|

The NE555D is a precision timing circuits capable of producing accurate time delays or oscillation. In the time-delay or monostable mode of operation, the timed interval is controlled by a single external resistor and capacitor network. In the astable mode of operation, the frequency and duty cycle can be controlled independently with two external resistors and a single external capacitor. The threshold and trigger levels normally are two-thirds and one-third, respectively, of VCC. These levels can be altered by use of the control voltage terminal. When the trigger input falls below the trigger level, the flip-flop is set, and the output goes high. If the trigger input is above the trigger level and the threshold input is above the threshold level, the flip-flop is reset and the output is low.

Note: Image may vary from actual product in terms of Manufacturer/Brand name according to the availability.

Features:

- Timing from microseconds to hours

- A stable or monostable operation

- Adjustable duty cycle

- TTL compatible output can sink or source up to 200mA

- Applications: Clock & Timing, Consumer Electronics, Aerospace, Defence, Military, Embedded Design & Development

Package Includes:

1 x NE555DR SOIC-8 Timer (Pack of 5 ICs)

| | | Excellent chip to create multiple outputs from limited IO pins of microcontrollers.

The 74HC595; 74HCT595 is an 8-bit serial-in/serial or parallel-out shift register with a storage register and 3-state outputs. Both the shift and storage register have separate clocks. The device features a serial input (DS) and a serial output (Q7S) to enable cascading and an asynchronous reset MR input. A LOW on MR will reset the shift register. Data is shifted on the LOW-to-HIGH transitions of the SHCP input. The data in the shift register is transferred to the storage register on a LOW-to-HIGH transition of the STCP input. If both clocks are connected together, the shift register will always be one clock pulse ahead of the storage register. Data in the storage register appears at the output whenever the output enable input (OE) is LOW. A HIGH on OE causes the outputs to assume a high-impedance OFF-state. Operation of the OE input does not affect the state of the registers. Inputs include clamp diodes. This enables the use of current limiting resistors to interface inputs to voltages in excess of VCC. |